가산기

덤프버전 :

분류

1. 설명[편집]

加算器 / adder

컴퓨터에서 쓰이는 연산 장치(CPU)의 하나로 주로 하는건 제어 장치의 명령으로 2진수의 덧셈을 수행한다. 디지털 전자식 계산장치의 모든 수학연산에 사용되는 기초적인 소자다. CPU를 비롯한 연산제어장치는 가산기와 같은 여러 종류의 회로로 구성된다. 디지털이 아닌 아날로그 회로에서도 가산기 혹은 가산증폭기라 부르는 회로가 있는데, 입력 전압을 적절히 스케일링해서 더해주는 연산을 수행한다.

2. 대표적 종류[편집]

논리회로를 공부하다보면 대표적으로 보게되는 몇몇 종류가 있다. 대표적으로는 반가산기, 전가산기, 리플 캐리 가산기, 자리올림 예측 가산기(Carry Look ahead adder), 자리올림 저장 가산기(Carry save adder) 등이 있다.

2.1. 1비트 가산기[편집]

2.1.1. 반가산기[편집]

Half adder 라고 부르는 가장 간단한 형태의 가산기로, 진리표에서 Sum부분은 A와 B의 XOR을 따르며 Carry는 AND를 따른다.

캐리 올림이 없는 특수한 경우에만 사용할 수 있기에, 실제로 이 형태로는 거의 사용되지 않는다.

2.1.2. 전가산기[편집]

하단에 언급되는 모든 멀티 비트 가산기의 기본이 되는 회로이다. 반가산기 2개와 OR게이트 1개로 구성이 가능한 가산기로, 하위에서 올라온 자리올림수를 포함하여 계산하는것으로, 진리표가 복잡하다고 느낄 수 있지만 그냥 2진수 연산을 한다고 생각하면 쉽게 기억할 수 있다. A, B, 그리고 하위 자리올림수를 모두 0, 1이라는 이진수의 숫자로 보고 그 산술합을 계산해서 0이면 S도 0, C도 0이고, 1이면 S는1, C는 0, 2(이진수로 10)이면 S는 0, C는 1, 3(이진수로 11)이면 S는 1, C도 1이 되는 형식. 즉, C는 둘째자리, S는 첫째자리수를 따른다고 생각하면 편하다. 사실 sum과 carry의 정의를 생각하면 당연하다. 진리표를 포함해 그림으로 좀 더 도식화 한 형태는 다음과 같다.

온전하게 이진수 한 자리수의 덧셈 연산이 가능하기에 full adder (전가산기)라고 부른다. 좀 더 일반적이게는 3개의 입력 중 1이 몇개가 있는지 카운팅 한 후 그 결과값을 2비트 바이너리 수로 출력하는 회로이기 때문에 (3,2) counter라고도 부른다.[1]

2.2. 멀티 비트 가산기[편집]

컴퓨터는 8비트, 16비트, 32비트, 64비트등의 데이터 단위로 움직이기에, 가산기도 이에 대응하여 멀티 비트를 처리할 수 있어야 한다. 기본적으로 전가산기를 여러개 묶어서 사용한다.

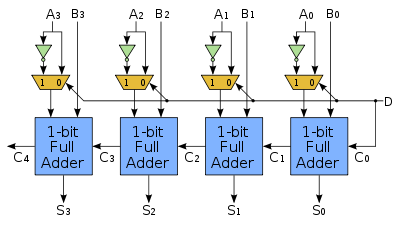

2.2.1. 리플 캐리 가산기[편집]

Ripple-carry adder

전가산기를 여러개 합쳐서 임의의 비트 수 연산이 가능하게 구성한 회로로 구조가 간단하다. 구성은 매우 간단한데, 각 비트를 전가산기로 구성한 다음 다음 자리의 올림수로 이전 자리 전가산기의 2번째 자릿수를 쓴다. 초등학교에서 덧셈을 배울 때 자릿수 하나하나마다 계산을 하고 자리올림을 하는 것과 같다.

그러나 비트 수가 길수록 아래 자리에서 올림수가 있는지에 대한 판단을 먼저 선행해야함으로 연산이 느려지는 단점이 있다. 예를 들어 32bit 덧셈을 리플 캐리로 수행할 경우, 2번째 자리를 계산하기 위해서는 1번째 자리의 올림수가 계산되어야 하고, 3번째 자리를 계산하기 위해서는 2번째 자리의 올림수가 계산되어야 하고 그걸 하기 위해서 1번째 자리의 올림수가 또 계산되어야 하고...... 하는 과정이 반복되어 결국 32번째 자리의 경우 자리 올림을 31번이나 반복해야 하기 때문에 속도가 굉장히 느려진다.

2.2.2. 자리올림 예측 가산기[편집]

Carry Look-ahead adder

리플 캐리 가산기는 자리수가 많으면 자리올림(캐리) 계산이 느려지는 문제가 있기에, 캐리를 별도의 로직으로 미리 계산해서 처리하는 방식이다. 별도의 회로가 필요하지만, 처리를 위해 거쳐야 할 게이트 수(Critical Path)는 그만큼 줄어드므로 계산속도는 그만큼 빨라진다.

자리올림 예측 가산기의 원리는 다음과 같다. 캐리가 C인 가산기가 임의의 두 비트(A, B)를 입력받았을 때 여기에서 자리올림(캐리)이 발생할 가능성을 생각해보자. 비트가 둘 다 1일 경우 캐리로 뭐가 들어오든 100% 캐리가 발생한다. 비트 둘 중 하나가 1이고 다른 하나가 0일 경우 다음에 들어오는 캐리에 따라 캐리가 발생할 가능성이 생긴다. 이 둘을 각각 G(Generation), P(Propagation)라고 지정하여 G = A and B, P = A xor B로 설계할 수 있다. 이 경우 캐리가 발생할 가능성은 G가 1이거나, 혹은 P와 C가 둘 다 1인 경우이므로 이 가산기에서 생성되는 캐리는 G or (P and C)라고 예측할 수 있다. 이 때 모든 자릿수의 G와 P를 한꺼번에 입력받는 Carry Lookahead 회로를 만들어, 입력받은 G와 P로 캐리를 생성한다.

얼핏 보면 복잡해보이지만 일괄 XOR 회로 처리는 2 Gate만에 할 수 있으므로 리플 캐리 가산기에서는 n bit의 캐리 계산을 위해 3n 번의 Gate를 거쳐야 했던 것과 달리 자리올림 예측 가산기에서는 비트가 몇이든 P를 계산하기 위한 3 Gate + C를 계산하기 위한 3 Gate = 6 Gate로 캐리 계산을 마칠 수 있다.

2.2.3. 자리올림 저장 가산기[편집]

Carry save adder

두 수의 각각의 비트는 전가산기를 거치게 하고, 이 중간 결과를 리플 캐리 가산기로 돌려서 최종 결과를 뽑아내는 방식이다.

이 자체로는 크게 성능향상이 있다고 할순 없지만, CSA 는 피연산자가 여러개일 때는 병렬성을 이용해서 계산 성능을 크게 향상시킬 수 있다는 장점이 있다. 특히 곱셈 연산을 하려면 피연산자가 여러개인 덧셈 연산을 해야 하기 때문에 곱셈기를 설계할 때 중요하게 다뤄지는 가산기이다. 대표적인 최적화 방식으로 Wallace tree가 있다.

2.2.4. 그외 다양한 가산기[편집]

문서 참조

비트 수가 32비트나 64비트 정도 되면 리플 캐리 가산기로는 답이 없고, CLA 을 사용하려 해도 Carry Look-ahead 로직이 너무 복잡해 져서 배보다 배꼽이 더 큰 상황이 발생한다. Carry Look-ahead 로직을 블록 단위로 쪼갠뒤, 이를 다단계로 구성하는 방법을 사용해서 성능을 향상시키는 등 여러 방안이 제시되었다.

2.2.5. Arithmetic Logic Unit[편집]

컴퓨터에서 뺄셈 연산은 '2의 보수'를 이용하여 구현하는데, 이 특성을 이용하면, 간단한 로직만 추가하며 가산기를 감산기로 사용하는 것이 가능하다. 이 뿐만 아니라 1을 증가시키거나(INC), 1를 감소하는 연산(DEC), AND / OR / NOT / XOR 연산, 시프트 / 로테이트 연산 등을 조합하여 계산 전용 로직을 만들 수 있다. 실제로 컴퓨터에서는 곱셈, 나눗셈 등의 다양한 연산을 하나의 로직에서 모두 처리해 버리는데 이를 ALU(Arithmetic Logic Unit) 라고 부른다.

원래는 ALU 는 원래 정수 연산만 취급했고, 실수 연산은 여러번의 정수연산으로 나눠서 처리했었다. 그런데 이렇게 하면 성능문제가 발생하니, 실수 연산을 위한 전용 모듈을 탑재하는데 이것이 FPU (Floating-Point Unit) 이다. 참고로, 인텔의 80386 CPU 에는 FPU 가 없었으며, 별도의 FPU Co-processor인 '80387'을 추가 장작해야 했다. 그 이후 나온 80486 부터는 FPU 가 Co-processor로서 기본 장착되었고, 다음 세대인 펜티엄부터 CPU 안에 내장되었다.

멀티코어 프로세서는 이 ALU가 복수 장착되어 있으며, SMT를 이용해서 한 ALU에 여러 연산을 처리할 수도 있다.

3. 계산기와의 차이[편집]

가산기는 2진수의 덧셈에 사용되는 논리 회로로, 기(器)라는 한자가 들어가기는 하나 독립적으로 작동하는 기계를 말하는 것이 아니다. 버튼으로 숫자를 입력하는 기계인 계산기와는 전혀 다른 것이다. 물론 전자식 계산기의 논리회로 중에 가산기가 반드시 포함되어 있다.

- 물리적인 차이

- 계산기는 완제품으로서 물리적인 크기를 가진다.

- 가산기는 논리회로로서 정해진 크기가 없는 가상적인 개념이다. 실제로는 어떤 형태로도 만들 수 있다.

- 하는 연산과 목적이 다르다.

- 계산기는 덧셈, 곱셈 등 다양한 명령을 받아 그 결과를 출력한다.

- 가산기는 일련의 연산에 필요한 덧셈 연산을 수행하여 결과값을 반환한다.

연산회로의 일부분으로 사용되므로 가산기에 직접 덧셈 명령을 내리는 것은 불가능하다.

이 문서의 내용 중 전체 또는 일부는 2023-11-09 04:09:19에 나무위키 가산기 문서에서 가져왔습니다.

이 문서의 내용 중 전체 또는 일부는 2023-11-09 04:09:19에 나무위키 가산기 문서에서 가져왔습니다.[1] 같은 논리로 반가산기는 (2,2) counter라고 부를 수 있으며, 그 외에도 (7,3) counter, (4;2) compressor, (7;2) compressor, (15,4) counter, (5,5,2) counter와 같은 회로들이 존재하며, 자리올림 저장 가산기(CSA)에서 중요하게 다뤄진다.